之前的文章“如何理解虚无缥缈的ESD”,有兄弟留言有没有ESD放电的仿真,其实发文前我找过,没找到,所以那篇文章里面的仿真是笼统的给了个信号源,然后按照频谱的方式来分析的。

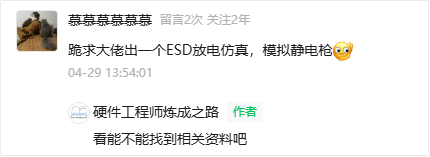

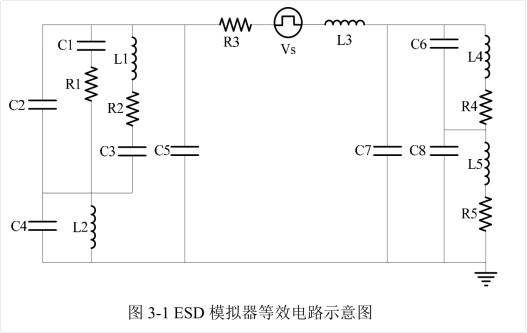

发完后我又查了些资料,终于算是有所得,找到了一篇硕士研究生论文《ESD 模拟器的特性仿真及实验验证》,作者是武汉理工大学 ——舒晓榕。里面有仿真模型,我用我常用的仿真软件LTspice试了下,确实是那么回事,现在就分享给兄弟们。原论文仿真电路模型 原论文的电路模型如下图:

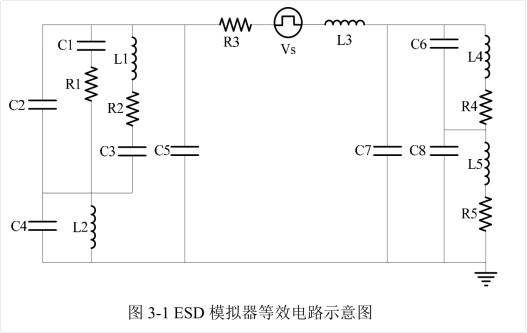

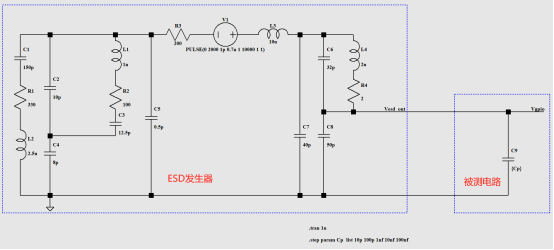

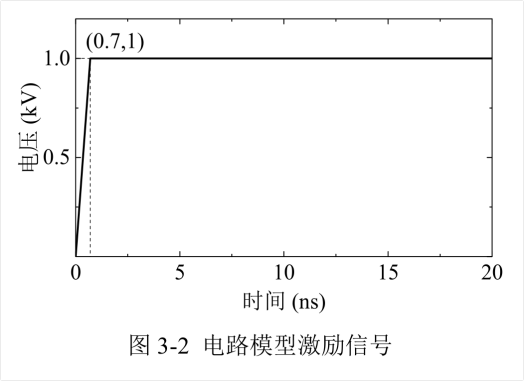

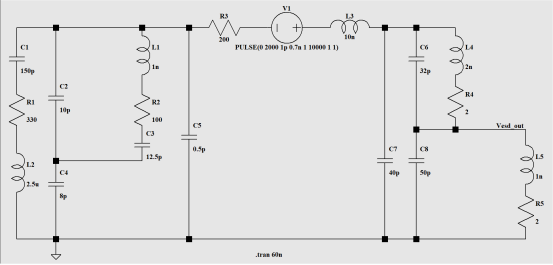

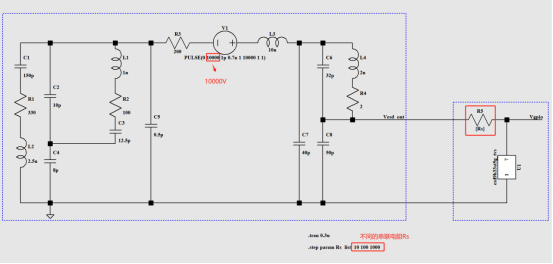

图 3-1 中,R1 和 C1 分别为 330 Ω 放电电阻和 150 pF 储能电容,为基于人体-金属模型的 ESD 模拟器基本放电电路。L1,R2 和 C3 为 ESD 模拟器枪体其它部件的等效电阻和等效电容。C2 为枪体内的寄生电容,L2 为接地带电感,C4为接地带对地电容。C5 和 C7 为枪体不同部位的对地电容。L3 和 R3 为继电器电感和电阻。L4 和 R4 为放电尖端电感和电阻,C6 则为放电尖端和电流靶间的电容。L5 和 R5 为电流靶电感及电阻,C8 为放电尖端对地电容。仿真得到的放电电流为 R5 元器件上的电流。电压源sV 为上升时间为 700 ps 的阶跃函数,且阶跃信号幅值等于放电电压。1 kV 放电电压时的激励信号见图 3-2。

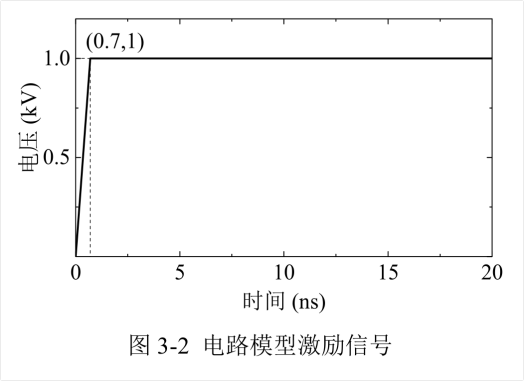

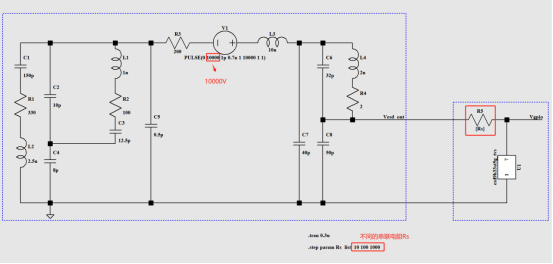

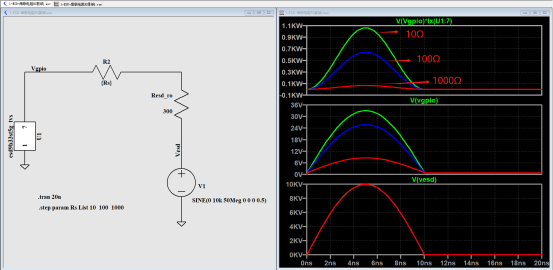

按照论文的模型和提供的参数值,用LTspice仿真了下,确实是符合IEC 61000-4-2标准放电波形的。 LTspice仿真验证 仿真原理图如下图:

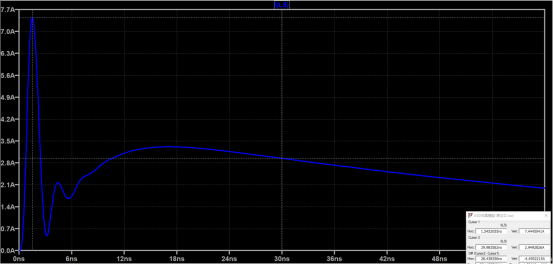

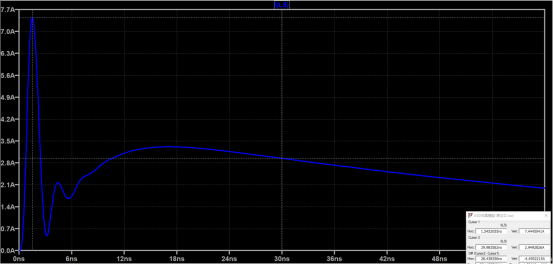

2Ω靶电阻上电流波形如下图

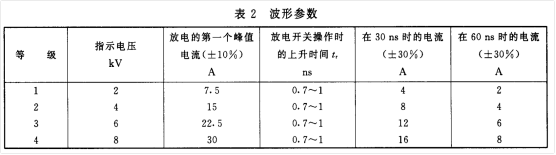

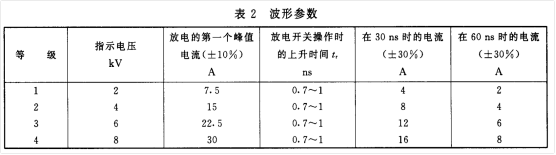

从仿真图上可以看到,仿真得到相关参数如下:峰值电流:7.4A上升时间tr:0.85ns(10%峰值到90%峰值)30ns处电流幅度:2.95A60ns处电流幅度:1.98A 对比规范里面的要求如下:

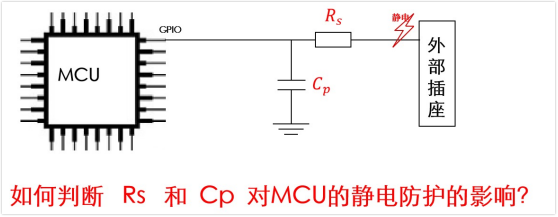

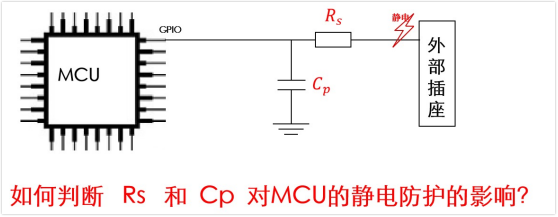

可以看到,2000V ESD测试时,几个参数都能很好的符合规范,除了30ns处的电流幅度规范里面是4A,仿真是2.95A,看着差得有点多,不过其实也是符合规范的。规范要求4A±30%,也就是电流范围是:2.8A~5.2A。2.95A在这个范围,所以也是符合规范的。 原来文章的问题 在之前的文章“如何理解虚无缥缈的ESD”里面,我曾猜测ESD的典型波形可能是直接输出短路的时候测的,现在看来,其实是有误的,至少从论文里面看来应该是输出接2Ω电阻+1nh电感串联。 不过我仿真看了,用这个电路将输出短路,其电流波形也基本不变,只是峰值输出电流小了一点,从7.5A降低到了7.0A,对分析结果影响不大。 另外,现在既然有了更为真实的ESD模型,我们就把原来文章的问题用新的方法再仿真看看。 老问题——为什么串电阻和并联电容能够改善 ESD? 也就是下面这个问题:

a、我们先来看滤波电容 Cp 的值对静电防护的影响

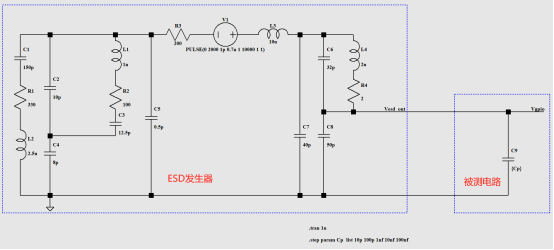

构建电路如下图,左边是ESD发生器(去掉了2欧姆靶电阻和1nh靶电感),右边是被测电路。

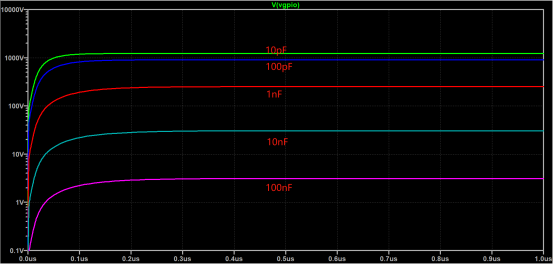

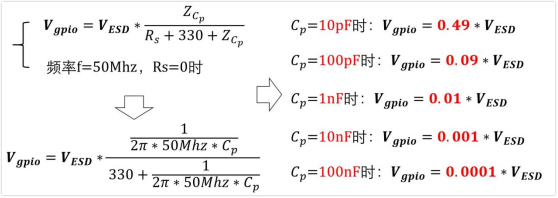

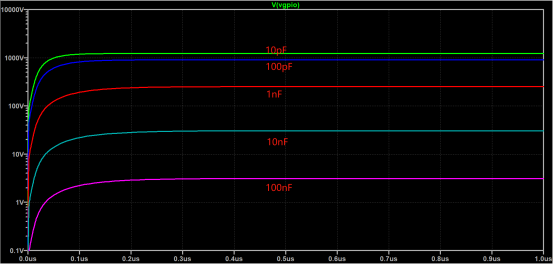

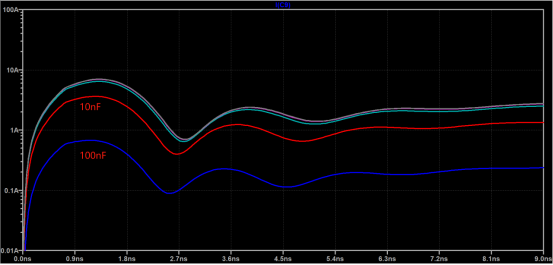

因为我们是为了看电容的影响,所以排除Rs的影响,将设置Rs=0。电容Cp参数分别为:10p,100p,1nf ,10nf,100nf,我们看残压Vgpio电压值如下图:

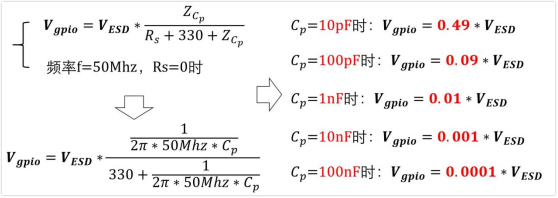

我们可以读出不同电容情况下Vgpio的最大值电压:10pF时Vgpio最大值=1220V100pF时Vgpio最大值=903V1nF时Vgpio最大值=251V10nF时Vgpio最大值=30V100nF时Vgpio最大值=3V 对比下之前文章的结果:

我们代入 ESD 2kV的测试情况,就可以得到不同Vgpio的电压值:10pF时Vgpio最大值=980V100pF时Vgpio最大值=180V1nF时Vgpio最大值=20V10nF时Vgpio最大值=2V100nF时Vgpio最大值=0.2V 为了方便对比,就列个表直接看下现在新模型的结果和之前的结果:电容值 | 新ESD放电模型2000V测试结果 | 之前文章的频谱分析法2000V结果 |

Cp=10pF | 1220V | 980V |

Cp=100pF | 903V | 180V |

Cp=1nF | 251V | 20V |

Cp=10nF | 30V | 2V |

Cp=100nF | 3V | 0.2V |

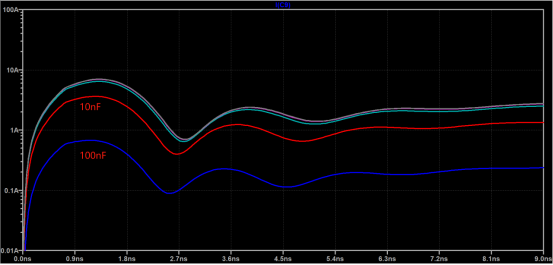

通过对比我们发现,如果只是定性分析,残压Vgpio都是随电容值增大而迅速下降,说明加电容确实对 ESD有用。不过如果定量看的话,二者差异还是很大的,特别是在100nF时,新模型残压是3V,而老的方法只有0.2V,差了十几倍。 为什么会这样呢?到底之前准确还是现在准确? 个人认为,这是因为之前老的方法是从频谱的角度来分析的,而频谱是按照典型放电电流波形来的。而现实的情况是,不同的负载(对不同的东西放电),放电的电流波形肯定是有差异的,之前的模型因其本身假设的局限性,我们得到的结果自然是粗糙的。 因此,总的来说,我认为这个新的模型是更准确的。 下面是新模型静电放电时对应的放电电流波形,可以看到,这个波形和静电放电的典型电流波形差异还是挺大的。由此说明,给不同的负载放电,静电放电电流波形是不同的。

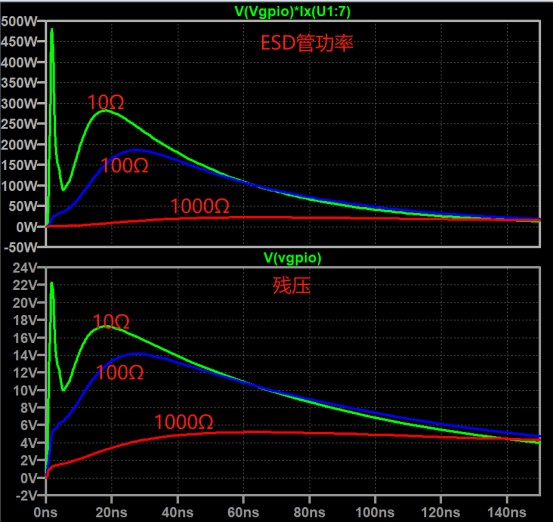

b、串联电阻 Rs 的影响 看完电容的影响,我们再来看下电阻的影响。因为如果MCU输入电阻看作无穷大的话,是无法发生静电放电的,所以我们要结合更真实的情况,在 MCU 那里放个 ESD 管,看这个管子承受的功率以及残压Vgpio大小就行。 为了方便和之前的结果做对比,静电放电电压设置为10000V,仿真电路图如下图:

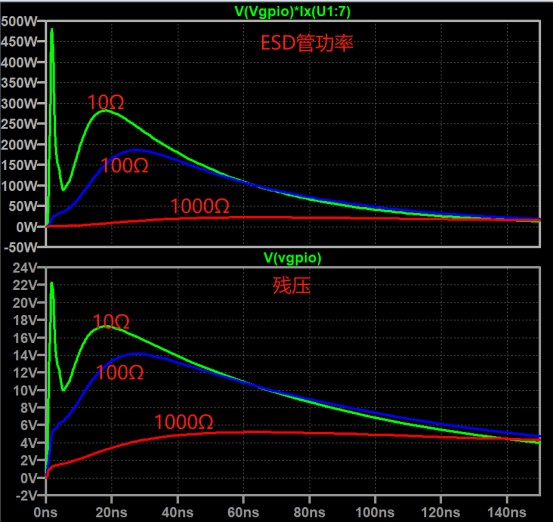

仿真结果如下图:

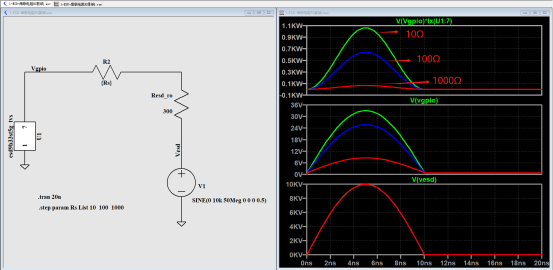

对比下之前简易模型的文章的结果:

可以看到,简易模型和现在新的模型,功率值和残压同样都有差异,但是如果仅仅是定性分析的话,我们都可以很清晰的看到不同电阻对ESD放电的影响,二者都能说明串联电阻越大,对ESD防护越有好处。 小结 通过查询论文,我终于找到了可以在LTspice里面进行仿真ESD的电路了,并且我又将之前的问题用新的模型分析了一下。从结果来说,新的模型更为准确。但是也不能说之前文章写的东西是错误的,只能说它模型简单,精度不高。 并且 ,如果从分析具体问题的角度,其实之前的文章“如何理解虚无缥缈的ESD”应该更容易理解,毕竟,我们不可能一遇到问题就拿这个精确的模型去实际仿真下,有时候我们仅仅只需要在脑子里面过一下,定性分析下就足够了。 仿真源文件下载 仿真文件我放置到了网盘,有需要的自提。下载方法:关注我的微信公众号“硬件工程师炼成之路”,在后台回复“炼成之路Pro”,就可以下载了,放置在目录:炼成之路Pro-->01-ESD仿真模型

论文文件我没有提供,怕侵权,就只告诉兄弟们论文名称了——《ESD 模拟器的特性仿真及实验验证》,作者是武汉理工大学 ——舒晓榕,我相信真正需要的兄弟应该能自己想到办法搞到。 声明:以上内容仅是个人观点,不保证正确性,如有问题,请留言指出。 *博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。