今天说下上一期留下的问题:

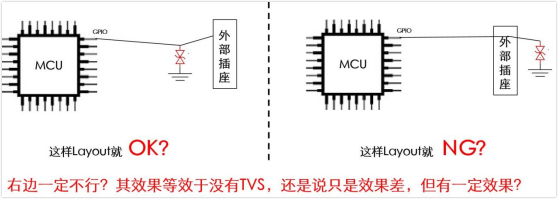

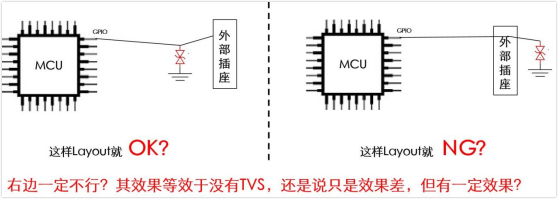

都说接口处的信号要先过ESD/TVS管,然后拉到被保护器件,为什么不这样做效果就不好?那如果受板子实际情况限制,必须这样layout,是一定不行吗?

在这之前呢,如果没看过上一期文章“如何理解虚无缥缈的ESD”,建议先看一看,因为这篇是以上一篇的观点为基础的。

硬件工程师炼成之路一个从业十多年的有追求的硬件工程师,我的追求:知其然并知其所以然。代表作有《硬件工程师炼成之路笔记》,《硬件工程师炼成之路器件篇》156篇原创内容公众号

为什么有上面这个问题? 有这个问题的原因,我觉得主要是因为两点。 一是因为从原理图上看来,二者并没有区别,都是ESD管接在同一个网络GPIO上面。既然没有区别,那为什么结果会有差异呢?对于新手来说,确实难以理解。 二是既然跟layout有关,那两种不同的layout方式?到底是影响了什么参数造成了这个差异呢?这些网上也没有找到相关的较深入的文章。 问题的原因——走线电感 我们设想的是,放电时,静电能量都从ESD管这里泄放掉,而不通过我们的芯片放电,这样才能实现ESD管保护芯片的目的。

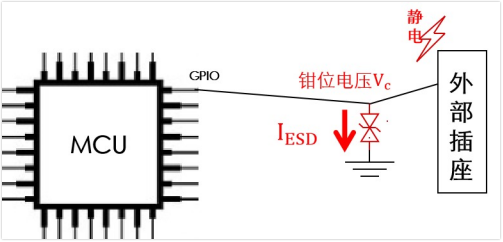

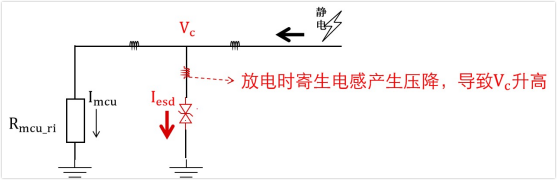

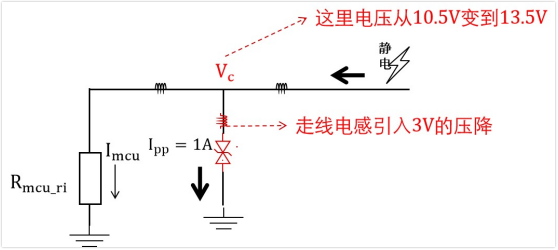

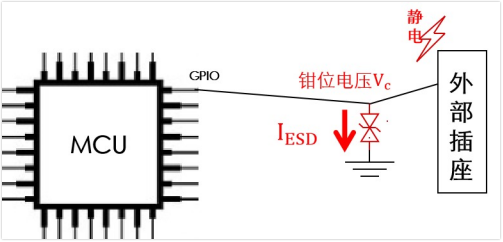

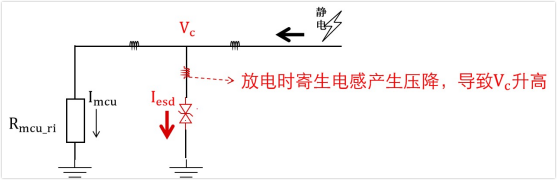

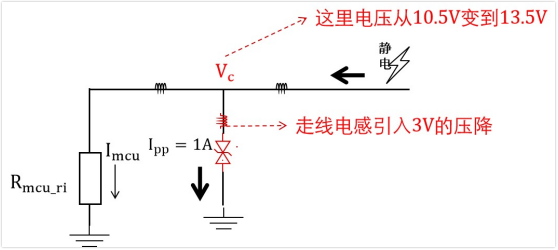

如上图,理想情况下,如果ESD管的钳位电压足够低,那么静电放电电流基本都从ESD管进行泄放。问题是,我们通常要通过PCB实现这个电路,PCB Layout走线也不是理想的,会有走线电感。

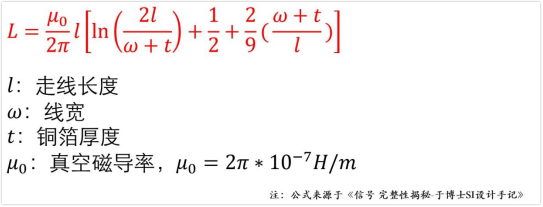

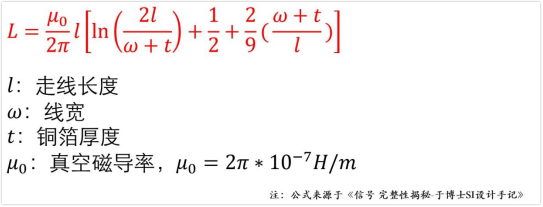

上一期我们知道,ESD放电时信号频谱带宽是几十Mhz到500Mhz,是高频的,而电感是频率越高,阻抗越大。如果Layout引入寄生电感,ESD泄放的时候电流也会在电感上面形成压降,导致芯片端残压升高,如果电压高于了芯片的耐受电压,那么就会击穿芯片,导致防护失败。 上面说法还是笼统,下面我们拿数据说话。 走线电感的阻抗 很多人可能会认为走线电感,那不就是寄生电感吗,听起来就很小,不能直接忽略吗?能不能忽略自然就是看影响,只有没影响的情况下才能忽略,那到底能不能忽略呢? PCB的走线电感是可以计算的,就是用下面这个公式:

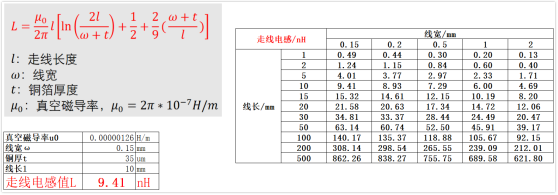

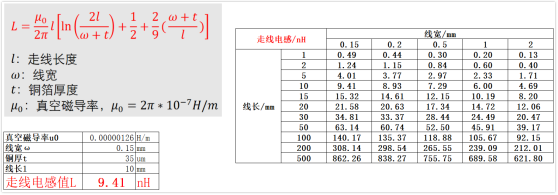

套用这个公式,可以得到走线长度1cm,宽度为6mil,铜厚为1oz的走线电感为9.41nH。

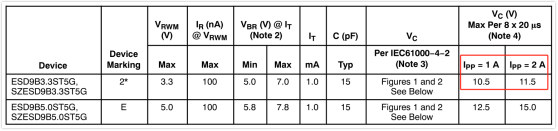

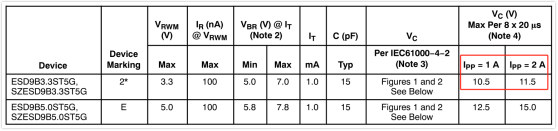

上面这个表格是我自己做了个excel表格,文末会分享给兄弟们,可以在excel里面输入对应的线宽,铜厚,线长等参数,然后就可以得到对应的电感值了,也可以看右边的表格做一个快速的估算。 好了,现在电感值已经有了,是9.41nH,我们根据公式ZL=jwL=2πfL,得到在50Mhz(ESD放电波形电流频谱是几十Mhz到500Mhz,貌似(不太确定)ESD释放时能量主要集中在几十Mhz这个频率,所以取50Mhz)时的阻抗ZL(50Mhz)=2*π*50Mhz*9.41nH≈3Ω。 电感走线阻抗已经知道了,那么影响到底有多大呢? 电感的影响 我们以3.3V ESD器件esd9b33st5g为例子,如下图。

如果我们是理想Layout 的情况下(没有寄生电感),那么在ESD管泄放电流Ipp为1A的时候,钳位电压为10.5V。而如果现在Layout不好,引入了寄生电感,其50Mhz时等效阻抗为3欧姆,如果电流依然是1A,那么电感上面的压降就是3V,这样导致整体看起来,钳位电压从10.5V提到到13.5V。

以上举的是6mil,10mm的走线长度,这个走线长度已经是非常小的了,可以看到,它已经对我们的ESD性能造成了影响。 如果长度增加到10cm,从上表知道,走线电感就是140nh,50Mhz对应阻抗是ZL(50Mhz)=2*π*50Mhz*140nH≈43Ω,同样的方法得到1A定流时的等效钳位电压VC=53.5V,这是我们说这个ESD完全没用应该是没毛病的。 小结 本文主要说下自己对于ESD管的Layout要求的理解,主要从寄生电感的角度来说的,虽说文章有一些数据,但是整体还算是定性分析。实际情况是更为复杂的,比如说ESD管到MCU也有走线,也有寄生电感,这对ESD更为友好一点。还有就是如果寄生电感大了,ESD的泄放电流应该也会小一些,而我上面的数据都是假设Ipp是1A时的。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

硬件工程师炼成之路一个从业十多年的有追求的硬件工程师,我的追求:知其然并知其所以然。代表作有《硬件工程师炼成之路笔记》,《硬件工程师炼成之路器件篇》156篇原创内容公众号

硬件工程师炼成之路一个从业十多年的有追求的硬件工程师,我的追求:知其然并知其所以然。代表作有《硬件工程师炼成之路笔记》,《硬件工程师炼成之路器件篇》156篇原创内容公众号